Появление первых данных о новых

процессорах Intel следующего поколения для корпоративных систем в рамках платформы Haswell-EP, запланированных к выпуску в период 2013-2014 гг, свидетельствуют о том, что колоссальные усилия крупных игроков на рынке DRAM-памяти по продвижению нового типа оперативной памяти

DDR4, по-видимому, начинают приносить плоды. В СМИ просочились три весьма информативных слайда, раскрывающих компоновку платформы, структуру процессорного компонента и краткое описание функционала платформы. Процессоры Haswell-EP будут создаваться с применением 22-нанометровых проектных норм и, вероятно, будут первыми CPU c поддержкой памяти нового типа.

Первый и самый важный слайд даёт представление о структурной организации ключевых компонентов платформы, которая во многом аналогична

компоновке современной платформы Sandy Bridge-EP, где n-количество процессорных разъёмов сообщаются друг с другом посредством быстрой шины QuickPath Interconnect (QPI). Intel планирует использовать 2-канальный интерфейс QPI, позволяющий вдвое увеличить пропускную способность интерфейса в сравнении с корпоративными платформами текущего поколения. С учётом полосы пропускания каждого канала в 6.4 Гигатрансферов в секунду максимальная суммарная пропускная способность шины составит 51,2 Гбайт/сек.

Каждый сокет позволит работать с 4-мя каналами памяти DRAM DDR4, спецификация которой предполагает коренное изменение топологии работы в связи с внедрением конфигурации типа «точка-точка». Хотя теперь каждый канал от контроллера памяти ограничится поддержкой не более одного

модуля памяти, производители памяти получат бо́льшую свободу действий в плане масштабирования объёмов планок памяти в результате совершенствования технологии и улучшение методов производства микросхем памяти. Аналогично процессорам Sandy Bridge-EP процессоры Haswell-EP возьмут на себя основную ответственность за функционал линий PCI-Express, который ляжет на плечи так называемых системных агентов, при этом отвечать за работу с периферийными устройствами будет чипсет.

Одно значительное и весьма актуальное нововведение предполагает отказ от использования сетевого интерфейса в рамках стандарта Gigabit Ethernet. Ожидается, что к моменту выхода Haswell-EP данный стандарт с пропускной способностью 1 Гбит/сек потеряет актуальность, по крайней мере, в корпоративном сегменте, где общепринятыми станут более быстрые технологии, такие как 10 Gigabit Ethernet или даже InfiniBand. Ввиду «прожорливости» этих интерфейсов Intel подвергла платформу реструктуризации, с тем чтобы «обычные» встроенные сетевые интерфейсы были завязаны не на чипсете, а на контроллере PCI-E процессора.

Хотя следующий слайд не изобилует деталями о микроархитектуре, он тем не менее даёт достаточно полное представление о структуре чипа Haswell-EP, которая во многом аналогична структуре чипов Sandy Bridge-EP, за исключением, видимо, возросших возможностей по масштабированию. В самых общих чертах чип содержит дополняемые кэш-памятью третьего уровня общевычислительные ядра, блок под названием «Системный агент» (System Agent), интегрированный контроллер памяти, контроллер PCI-Express и контроллер шины QPI, связанные друг с другом кольцевой шиной (ring-bus). Включение/отключение компонентов осуществляется посредством манипуляций с контрольными точками (ring-stops – здесь шина берёт/отдаёт данные и инструкции) для каждого из компонентов, что позволяет создавать различные конфигурации чипа на базе единой схемы.

Как упоминалось ранее, процессоры Haswell-EP предполагают применение 22-нанометровой технологии, которая к моменту их появления на рынке достигнет определённой стадии зрелости. Хотя слайд не содержит указаний на конкретное число ядер, планируемых к реализации в рамках новой платформы, их количество, вероятно, составит 14. Такой вывод можно сделать, если указанный на слайде максимальный суммарный объём кэша L3 в 35 Мб поделить на объём кэш-памяти, выделяемый из расчёта на каждое ядро (~2560 Kб). Даже в современных процессорных архитектурах Intel кэш-память 3-го уровня не является монолитной, хотя её ресурсы используются всеми ядрами. Она поделена на сегменты, допускающие возможность манипуляций с целью изменения размера каша L3 в зависимости от конкретной модели CPU.

«Системный агент» берёт на себя бо́льшую часть вспомогательных функций процессорного компонента аппаратной платформы. Встроенный контроллер памяти (Integrated Memory Controller – IMC) поддерживает работу с памятью нового типа (DDR4), предлагающей возможность реализации более высоких скоростей и объёмов в сочетании с более низкими напряжениями питания (интегрированный в CPU Haswell-EP контроллер памяти поддерживает работу в 4-канальном режиме с памятью DDR4 на частоте 2133 МГц). Контроллер шины PCI-E, являющийся контроллером

PCI-Express Gen 3.0, позволяет задействовать 40 линий для платформы Haswell-EP и 24 линии в случае с платформой Haswell-EN.

Хотя все CPU на ядре Haswell-EP содержат шину DMI (Direct Media Interface) для связи с чипсетом, не все процессорные разъёмы на материнской плате будут напрямую сообщаться с чипсетом. Это объясняется применением ячеистой топологии. предполагающей связь сокетов друг с другом посредством линков QPI, при этом только один из процессоров будет работать с чипсетом по DMI-шине (и линкам PCI-Express, используемым в качестве вспомогательных для шины DMI, если такая схема может быть реализована).

Среди прочего слайд упоминает поддержку технологии виртуализации ядер HyperThreading, поддержку

режима работы P-state для каждого ядра, возможность масштабирования рабочих частот для неядерной части (Uncore), более современную версию технологии

Turbo Boost и встроенную логику управления питанием процессора (Voltage Regulator Module - VRM) более эффективного с экономической точки зрения типа VRD (Voltage Regulator Down), обладающего улучшенной вольт-амперной характеристикой, реализация которой позволит не беспокоиться по поводу совместимости материнских плат различных производителей по дизайну VRM. Процессоры Intel нового поколения обладают внушительным энергопотреблением в диапазоне 130~160 Вт.

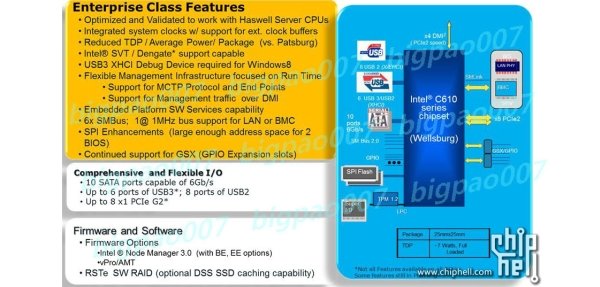

Другим крупным элементом платформы Haswell-EP является чипсет, получивший кодовое обозначение Wellsburg и маркетинговое название Intel C610. Здесь Intel намерена воспользоваться преимуществами нового техпроцесса (вероятнее всего, речь идёт о 32-нм проектных нормах), чтобы расширить компонентную базу чипа без необходимости увеличения его размеров. С этой целью производитель установил ограничения на размеры чипа (не более 25 x 25 мм) и на его энергопотребление (не более 7 Вт при максимальной нагрузке).

Чипсет содержит свой тактовый генератор, который может задавать рабочую частоту для других компонентов в составе платформы либо даже применяться для реализации схемы, предполагающей использование частот от внешнего тактового генератора в качестве базовых. В отношении интерфейсного функционала наблюдается более активное распространение интерфейсов нового поколения, включая

SATA 6 Gb/s и

USB 3.0 (SuperSpeed). Чипсет позволит задействовать не менее 10-ти портов SATA 6 Gb/s, а также обеспечит поддержку технологии Rapid Storage Technology RAID с возможностью использовать

SSD-накопитель в качестве быстрой кэш-памяти – аналогично технологии

Intel Smart Response. Чипсет C610 "Wellsburg" предлагает новый расклад USB-портов по схеме: “6 х USB 3.0 + 8 х USB 2.0”. Как напоминание о прошлом сохранён функционал Gigabit Ethernet в виде микрочипов PHY, который вряд ли найдёт применение в

серверных материнских платах основного сегмента, хотя модели начального уровня, вероятно, всё же воспользуются парой контроллеров Gigabit Ethernet. В заключение отметим, что Haswell-EP выглядит как мощная комплексная платформа, акцентирующая внимание на будущих сетевых интерфейсах с улучшенной полосой пропускания.

Подождите...

Подождите...